Difference between revisions of "XilinxEVB"

(→Download) |

|||

| (17 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

<center> | <center> | ||

| − | + | --- --- --- English: [[XilinxEVB/en]] Slovensky: [[XilinxEVB/sk]] --- --- --- | |

| − | |||

| − | |||

| − | [[ | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | [[ | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

</center> | </center> | ||

| − | + | {{Generic}} | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | <!-- Please do not edit this page, edit the language-specific subpages | |

| + | Prosim editujte podstranku pre prislusnu jazykovu verziu --> | ||

| − | + | {{Footer}} | |

| − | |||

| − | |||

| − | |||

| − | |||

Latest revision as of 23:13, 26 March 2008

--- --- --- English: XilinxEVB/en Slovensky: XilinxEVB/sk --- --- ---

<multilang> @en

Author: Juraj Michálek

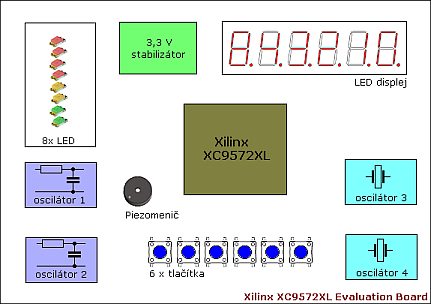

Xilinx Evaluation Board

Description

The purpose of this evaluation board (EVB) is to acquire experiences with the CPLD Xilinx family XC95xxXL. This board uses XC9572XL, which contains 72 cells. Their inerconnections gives the required function.

Peripheral:

6 multiplexed 7-seg LED display with power drivers enables to make a counter and other number displaying devices.

8 LEDs for differet signaling purposes, indicators of the internal states of the CPLD etc. LEDs are driven with ULN2803A transistor array with OC outputs. They can be used also for driving an external applications.

2 x non-symetrical RC oscillator using 74AC14 (U2). One of the oscillator enables frequency changing using the multiturn trimer. Both oscilator frequencies are controlled by an R and C components, according the f=1/(3RC) rule. Inhibit input can stip the oscillator (High level). Oscillator output is a cca 1:1 . Can be used as a clock source especially for "slow" applications.

2x hybrid XT oscillator, clock source for higher frequencies, especially for more precise and stable applications. Oscillator output is usually harmonic and it can be shaped to the rectangle using U1 Schmitt triggers.

6x pushbuttons. Spoločný vývod spínačov, ako aj spoločný vývod R-siete vyvedený na pinovú lištu, umožňuje nadstavenie aktívnej úrovne pri stlačení tlačítka. (teda či pri stlačení polezie do CPLD L alebo H. Tlačítka nie sú úmyselne ošetrené voči zákmitom. Toto ošetrenie je možné previesť priamo v CPLD (aspoň si to myslím ;-) )

Buzzer enables to create sound effects with the CPLD. Piezo buzzer without an internal oscillator is used. It is necessary to use a frequency signal to drive it. Pin liste enables to connect also the higher voltage than boards 3,3 V. Correction: it is necessary to connect a discharge resistor (cca 1k) paralell to the piezoelement. New version of the board already contains this resistor.

All the peripherals are disconnectable using DIP switches. This enables to use all the I/O Pins also for another special purposes. Pin contacts on each CPLD pin are used for interconnections or for logic probe or analyser connection.

EVB is powered from the external unstabilised power supply min. 5 Voltds. Required internal power supply 3,3 V is delivered from the LF33CV stabilisator. Power consumption depends on the CPLD operational frequency and on the peripheral activities. Filter F1 is for filtering disturbances, especially when powering from cheap wall adapters. It can be omitted. During the board population it is recommended pre-heating of the board e.g. hot air gun, otherwise the ground plane will drain most of soldering gun heat.

Board dimensions: 135 x 107 mm.

Contact: ICQ: 209 598 598 ; mail: evb.cpld@gmail.com

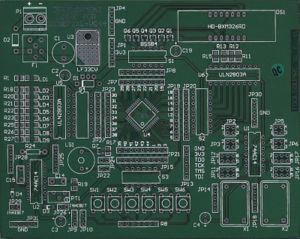

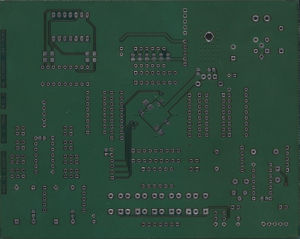

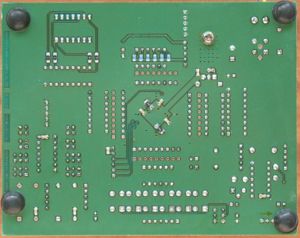

Images

Programmer

The board is to be programmed using the simple paralell port programmer.

Its schematic diagram is directly on the Xilinx webpage, or e.g. here also with the PCB.

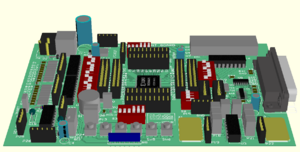

Xilinx EVB - new version

New version of the board uses the bigger CPLD (XC95144XL-TQ100). Also the JTAG LPT programmer is onboard and additional 8 LEDs is available. There is also a reduction for the XC9572XL PC44 chip. Another reductions are planned. Also the XC9572XL TQ100 chip can be used without problems.

Note: Instead 74HC family also the 74AC family can be used and vice versa.

3D model of the new version of the board:

Downloads

- Schematic diagram EVBXC9572XL in pdf format Media:schema.pdf

- Schematic diagram EVBXC95144XL in pdf format Media:schema95144XL.pdf

- Schéma a osadzovací plán redukcie PC44_TQ100 pre EVBXC95144XL vo formáte pdf Media:PC44_TQ100.pdf

- Population of the EVBXC9572XL Media:doska.pdf

- Population of the EVBXC95144XL Media:doska144.pdf

- Bill of Material Media:DB_XC9500XL_VQ44_rev0.xls

- Bill of Material for EVBXC95144XL Media:DB_XC95144XL_rev0.xls

Examples

- Abel: The simplest logic

- Abel: Stepper motor controller

- Abel: Stepper motor controller with microstepping

Links

- Short video

- Xilinx: The Programmable Logic Company

- XC9500XL Resources

- Digilent - boards producent, also the examples

- Open Cores (processors, communications,...)

@sk

Autor: Juraj Michálek

Xilinx Evaluation Board

Popis

Vývojová doska (ďalej len EVB) je určená na získanie skúseností s používaním CPLD Xilinx rady XC95xxXL. Na tejto doske je použitý obvod XC9572XL, obsahujúci 72 buniek, ktorých spájaním dosiahneme požadovanú funkciu obvodu.

Periférie: Skladba typu periférii vyplýva z určenia zariadenia pre základnú výuku.

6 miestny multiplexovaný 7segmentový LED displej s výkonovými budičmi umožňuje realizáciu čítača, prostého čítača a rôznych zapojení vyžadujúcich číselné zobrazenie.

8 ks LED pre realizáciu rôznych blikačov, alebo napr. indikaciu vnútorných stavov CPLD LED sú budené T-poľom ULN2803A s výstupom typu OC, čím je umožnené použitie týchto výstupov v externých výkonových aplikáciach.

2x nesymetrický RC oscilátor využívajúci 74AC14 (U2). Jeden z oscilátorov umožňuje plynulú zmenu frekvencie pomocou viacotáčkového trimra. Oba oscilátory sa ladia zmenou R a C prvkov, podľa vzorca f=1/(3RC). Vstup Inhibit umožňuje privedením kladného napätia zastaviť oscilátor. Výstupom oscilátora je obdĺžnikový signál so striedou cca 50%. Využiteľný ako zdroj signálu hodín, najmä pre "pomalobežné" aplikácie.

2x hybridný XT oscilátor, určený ako zdroj hodinového signálu vyšších frekvencií, alebo pre aplikácie s požadovanou presnosťou a stabilitou hod. signálu. Výstup z oscilátorov je väčšinou sínusový, jeho vytvarovanie na obdĺžnik je možné pomocou schmittových invertorov obsiahnutých v U1

6ks tlačítok. Spoločný vývod spínačov, ako aj spoločný vývod R-siete vyvedený na pinovú lištu, umožňuje nadstavenie aktívnej úrovne pri stlačení tlačítka. (teda či pri stlačení polezie do CPLD L alebo H. Tlačítka nie sú úmyselne ošetrené voči zákmitom. Toto ošetrenie je možné previesť priamo v CPLD (aspoň si to myslím ;-) )

Piezomenič umožňuje výrobu zvukových efektov pomocou CPLD. Jedná sa o typ bez vnútorného oscilátora, preto je nutné budenie frekvenciou. Pinová lišta umožňuje pripojiť piezomenič na vyššie napätie ako 3,3V ktoré poskytuje EVB. Oprava: paralelne k piezomeniču treba prispájkovať vybíjací rezistor (cca 1k), inak sa žiadne zvuky nekonajú. Nová verzia dosky ma už rezistor doplnený

Všetky periférie sú odpojiteľné pomocou DIP spínačov. Tým je umožnené v špeciálnych aplikáciach použitie I/O pinov CPLD aj na iné účely. Dva kontakty na každom pine CPLD (okrem napájacích) slúžia na prepojenie daného pinu CPLD s externou perifériou, alebo na pripojenie log. sondy, prípadne log. analyzátora.

EVB je napájaná z externého nestabilizovaného zdroja min 5V. Interné prevádzkové napätie 3,3V je stabilizované stabilizátorom LF33CV. Odber závisí na frekvencií s akou CPLD pracuje a aktivite periférií. Filter F1 slúži na filtráciu rušenia, najmä pri napájaní EVB z lacných impulzných adaptérov. Je možné ho nahradiť prepojkami. Pri osadzovaní EVB súčiastkami je vhodné jej zahriatie, napr teplovzdušnou pištoľou. Inak rozliata zemniaca plocha veľmi účinne odvádza teplo z hrotu spájkovačky. Rozmery dosky: 135 x 107 mm.

V zapojení nie sú použité žiadne nezohnatelné súčiastky. Až na CPLD sa všetky dajú kúpiť v SOS a GME. CPLD napríklad v Elbatex-e. F1 je k dostaniu v SOS pod číslom S085401, alebo do vyhľadávača zadajte BNX. DS1 maju zasa v GME pod číslom 512-925 (zeleny); 512-905 (cerveny).

Kontakt na autora: ICQ: 209 598 598 ; mail: evb.cpld@gmail.com

Obrázky

Programátor

Doska sa programuje jednoduchým programátorom ovládaným cez paralelný port.

Schéma zapojenia je na priamo na stránkach Xilinxu, alebo napr. tuto aj s plošákom.

Nová verzia vývojovej dosky

Od starej verzie sa doska odlišuje použitím väčšieho CPLD, a to XC95144XL-TQ100. Ďalšou zmenou je pridanie JTAG programátora s pripojením na LPT a rozšírenie periférií o 8 LED. K doske je navrhnutá redukcia umožňujúca použiť XC9572XL PC44. V prípade dostatočného záujmu budú k dispozícií aj iné redukcie. Na dosku je možné bez problémov osadiť aj XC9572XL TQ100

Poznámka ku konštrukcií: Miesto obvodov rady 74HC možno použiť obvody rady 74AC a naopak.

Zatiaľ aspoň foto 3D modelu novej dosky:

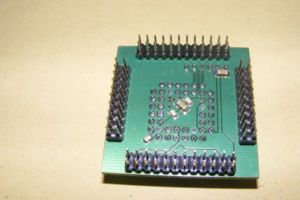

Foto osadenej redukcie. Umožňuje použiť obvod XC9572XL-PC44. Pri jej použití sú dostupné všetky periférie, okrem vrchného stĺpca LED.

Download

- Schéma zapojenia EVBXC9572XL vo formáte pdf Media:schema.pdf

- Schéma zapojenia EVBXC95144XL vo formáte pdf Media:schema95144XL.pdf

- Schéma a osadzovací plán redukcie PC44_TQ100 pre EVBXC95144XL vo formáte pdf Media:PC44_TQ100.pdf

- Osadzovací plán EVBXC9572XL Media:doska.pdf

- Osadzovací plán EVBXC95144XL Media:doska144.pdf

- Zoznam súčiastok (BOM) Media:DB_XC9500XL_VQ44_rev0.xls

- Zoznam súčiastok (BOM) pre EVBXC95144XL Media:DB_XC95144XL_rev0.xls

Príklady

- Abel: Jednoduchá logika

- Abel: Radič krokového motora

- Abel: Radič krokového motora s drobením kroku

Linky

- Krátke video

- Xilinx: The Programmable Logic Company

- XC9500XL Resources

- Digilent - vyrába dosky a sú tam príklady

- Open Cores (procesory, komunikacia, ...)

</multilang>

--- --- --- --- --- RoboWiki: (c) 2006 Robotika.sk --- --- --- --- ---